## Considerations on the development of an integrated electric inverter for high temperature applications

Yury Mikhaylov

Thesis submitted to the University of Nottingham for the degree of Doctor of Philosophy

2022

#### Abstract

The realization of integrated solutions for electric machine drives is a way to achieve higher space utilization in industrial and transportation electrical power applications. In some cases, limited space affects heat dissipation and the performance of a cooling system, so harsh operating conditions, i.e., high ambient (or cooling) temperature, are a possible additional requirement for integrated drivers. This research investigates in detail the design of some essential or sensitive parts of IMD, highlighting their behaviour under a high-temperature environment. An initial selection of switching power devices is a cornerstone of the inverter design that determines a number of crucial electrical, thermal, and mechanical parameters of the final assembly. Traditionally power modules or custom-designed power devices are the preferable choices for such challenging power electronics applications. An alternative approach based on the parallel connection of discrete MOSFET is underestimated by researchers and is less popular nowadays, although it can offer some valuable advantages. This work presents a comparative analysis of different power devices' packages with a generalized evaluation algorithm focusing on thermal and mechanical aspects in addition to conventional analysis of devices' electrical characteristics. The proposed method helps evaluate the range of feasible power density for PE and the drive itself. The results could give reference figures to demonstrate the capabilities of all popular power packages of novel SiC MOSFETs in the 2-level 3-phase inverter. In selecting power devices, special attention is paid to highlighting possible trade-offs between losses, junction temperature, and occupied volume. Another comparison analysis considers the characteristics of different capacitor materials under various operating conditions and evaluates the required volumetric parameters for DClink capacitor of the inverter. Several technical challenges related to the adoption and balancing of MOSFET parallel connection are discussed in the thesis. The possible protection of paralleled power devices against the crosstalk effect is studied in detail with a proposed simulation model of the gate driver circuit. Limitation of typical clamping methods if applied to parallel devices is demonstrated. The modified gate driver with a reduced current clamping path generates a lower voltage pulse and enhances the protection against spontaneous turn-on; its efficiency is verified by model simulation and experimentally. New thermal protection for current sensors, providing acceptable conditions up to 130C degrees of ambient temperature, is described and tested.

#### Acknowledgments

I'm incredibly grateful to my supervisors, Professor Giampaolo Buticchi and Professor Michael Galea, for their guidance, unwavering support, and encouragement in this challenging journey. I would like to express my deepest appreciation to my internal assessor Dr Chunyang Gu for providing technical expertise, sharing her knowledge, and for her great patience. Special thanks to Professor Carlo Cecati for spending his valuable time with me and for his constructive feedback on my work.

I thank my UK supervisor, Professor Pat Wheeler, for his help with thesis improvement and prompt feedback throughout this process. Many thanks to Dr Xiaochen Zhang for his unquestionable support throughout my study and for qualified technical and administrative assistance. I also would like to extend my sincere thanks to Professor He Zhang for developing a supportive team atmosphere and providing an excellent technical environment in the laboratory.

I could not have succeeded in my study without tremendous support from my family, especially my wife, who maintained my spirit and motivation high regardless of any troubles or falls.

#### List of publications

- Ahmed Aboelhassan, Yury Mikhaylov, Mukhammed Murataliyev, Ahmed M. Diab, ChungKet Thein, Giovanni Migliazza, Shou Wang, Xiaochen Zhang, Michele Degano, Giampaolo Buticchi, Michael Galea. Design and Implementation of Integrated Motor Drive for High-Speed Aerospace Applications. Under correction.

- Yury Mikhaylov, Ahmed Aboelhassan, Giampaolo Buticchi, Michael Galea. Considerations on the Development of High-power Density Inverters for highly integrated motor drives. Under correction.

- Yury Mikhaylov, Giampaolo Buticchi, Paolo Giangrande, Michael Galea, "A gate driver for parallel connected MOSFETs with crosstalk suppression". Submitted to Chinese Journal of Aeronautics. Under Review.

- Ahmed Aboelhassan, Shuo Wang, Yury Mikhaylov, Giampaolo Buticchi, Michael Galea, and Serhiy Bozhko. A Discontinuous Modulated Model Predictive Control for Low Inductance High-Speed Electric Drive Applications. Working paper

## Contents

| Abstr                                                                 | act                                                                                                                                                                                                                                                                                                                                                                                                      | 2                                                                        |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Ackn                                                                  | owledgments                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                                        |

| List o                                                                | f publications                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                        |

| Conte                                                                 | ents                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                        |

| List o                                                                | f figures                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                        |

| List o                                                                | f tables                                                                                                                                                                                                                                                                                                                                                                                                 | 15                                                                       |

| Intro                                                                 | duction                                                                                                                                                                                                                                                                                                                                                                                                  | 17                                                                       |

| 1.1                                                                   | Progress of electric transportation                                                                                                                                                                                                                                                                                                                                                                      | 17                                                                       |

| 1.2                                                                   | Integration concept in the design of a motor drive                                                                                                                                                                                                                                                                                                                                                       | 21                                                                       |

| 1.3                                                                   | High temperature issues and benefits                                                                                                                                                                                                                                                                                                                                                                     | 24                                                                       |

| 1.4                                                                   | Contribution of this study                                                                                                                                                                                                                                                                                                                                                                               |                                                                          |

| 1.5                                                                   | Structure of thesis                                                                                                                                                                                                                                                                                                                                                                                      | 27                                                                       |

|                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                          |

| 2 St                                                                  | tate of art in power electronics of IMD and related technologies                                                                                                                                                                                                                                                                                                                                         | 29                                                                       |

|                                                                       | tate of art in power electronics of IMD and related technologies<br>Integration and its recent trends in literature and industry                                                                                                                                                                                                                                                                         |                                                                          |

| 2.1                                                                   | •                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                       |

| 2.1                                                                   | Integration and its recent trends in literature and industry<br>Design procedures and algorithms                                                                                                                                                                                                                                                                                                         | 29<br>37                                                                 |

| <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul>                         | Integration and its recent trends in literature and industry<br>Design procedures and algorithms                                                                                                                                                                                                                                                                                                         | 29<br>37<br>38                                                           |

| <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li></ul>             | Integration and its recent trends in literature and industry<br>Design procedures and algorithms<br>Cooling technology in power electronics of IMD                                                                                                                                                                                                                                                       | 29<br>37<br>38<br>47                                                     |

| <ul><li>2.1</li><li>2.2</li><li>2.3</li><li>2.4</li><li>2.5</li></ul> | Integration and its recent trends in literature and industry<br>Design procedures and algorithms<br>Cooling technology in power electronics of IMD<br>High temperature power electronics in IMD.                                                                                                                                                                                                         | 29<br>37<br>38<br>47<br>50                                               |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br><b>3 P</b>                         | Integration and its recent trends in literature and industry<br>Design procedures and algorithms<br>Cooling technology in power electronics of IMD<br>High temperature power electronics in IMD<br>Conclusion                                                                                                                                                                                            | 29<br>37<br>38<br>47<br>50                                               |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br><b>3 P</b><br>gravime              | Integration and its recent trends in literature and industry<br>Design procedures and algorithms<br>Cooling technology in power electronics of IMD<br>High temperature power electronics in IMD<br>Conclusion                                                                                                                                                                                            | 29<br>37<br>38<br>47<br>50<br><b>n-oriented</b><br>52                    |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br><b>3 P</b><br><b>gravim</b><br>3.1 | Integration and its recent trends in literature and industry<br>Design procedures and algorithms<br>Cooling technology in power electronics of IMD<br>High temperature power electronics in IMD<br>Conclusion<br>erformance analysis of PE for optimized switch selection and integration<br>etric/volumetric theoretical model of IMD                                                                   | 29<br>37<br>38<br>47<br>50<br><b>n-oriented</b><br><b>52</b><br>52       |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br><b>3 P</b><br><b>gravim</b><br>3.1 | Integration and its recent trends in literature and industry<br>Design procedures and algorithms<br>Cooling technology in power electronics of IMD<br>High temperature power electronics in IMD<br>Conclusion<br>erformance analysis of PE for optimized switch selection and integration<br>etric/volumetric theoretical model of IMD<br>Inverter Topology<br>Power switches. Types and characteristics | 29<br>37<br>38<br>47<br>50<br><b>n-oriented</b><br><b>52</b><br>52<br>56 |

| 3     | 5 Effect of advanced thermal conductive materials and cooling techniques           | 96   |

|-------|------------------------------------------------------------------------------------|------|

| 3     | 5 Comparison of 2-level and 3-level inverters                                      | 97   |

| 3     | Power density analysis for integrated motor drive system                           | 103  |

| 3     | 3 DC-link capacitor sizing                                                         | 112  |

| 3     | O Chapter Summary                                                                  | 121  |

| 4     | Theoretical analysis of crosstalk signals in parallel connection of switching devi | ices |

| and g | te driver adopted for this connection.                                             | 122  |

| 4     | Negative consequences of fast switching process                                    | 122  |

| 4     | 2 Modelling of crosstalk for parallel connection of MOSFETs                        | 123  |

| 4     | 3 The gate driver design with crosstalk suppression                                | 131  |

| 4     | Chapter summary                                                                    | 138  |

| 5     | Modifications of commercial current sensor to increased temperature range.         | 139  |

| 5     | Current sensor in IMD design                                                       | 139  |

| 5     | 2 Close loop current sensor structure and its thermal management                   | 141  |

| 5     | 3 Improvement of sensor's cooling system                                           | 144  |

| 5     | Power supply and control for HS cooling system                                     | 154  |

| 5     | 5 Chapter summary                                                                  | 157  |

| 6     | Conclusion                                                                         | 158  |

| 6     | Main Contributions                                                                 | 158  |

| 6     | 2 Future research                                                                  | 160  |

| Ref   | erences                                                                            | 162  |

| Ap    | endix A                                                                            | 170  |

| Lis   | of Acronyms                                                                        | 172  |

| Lis   | of Symbols                                                                         | 174  |

## List of figures

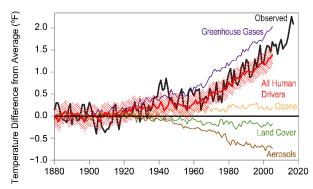

| Figure 1 – Increase in global temperature due to natural and human influences[1]17              |

|-------------------------------------------------------------------------------------------------|

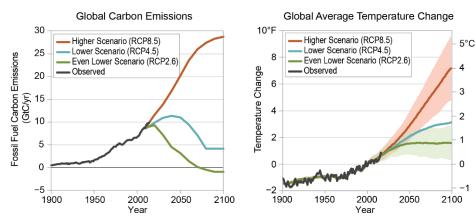

| Figure 2 - Observed and projected changes in carbon emissions and temperature[1]18              |

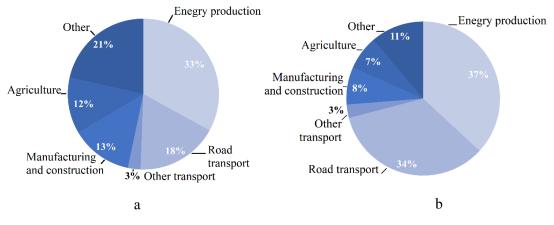

| Figure 3 - Total greenhouse gas emissions per sectors of human activity (a - world              |

| distribution, b – US distribution)                                                              |

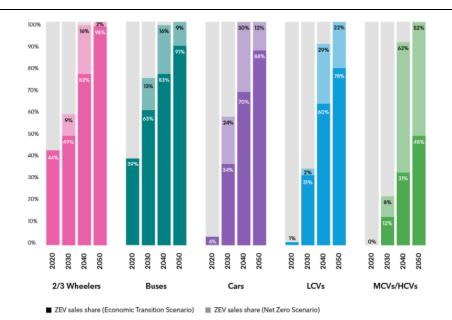

| Figure 4 – Forecast for sales share of EVs for period of 2020-2050 [5]                          |

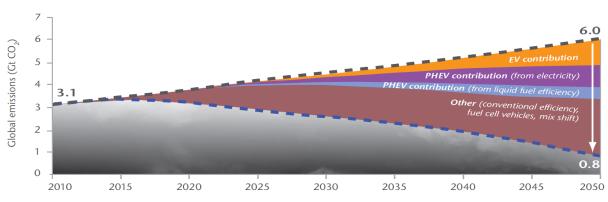

| Figure 5 – Forecast of possible reduction in $CO_2$ global emissions (in transportation) due to |

| development of different EV[6]20                                                                |

| Figure 6 - Step-by-step approach in the penetration of electrically-powered aircraft into the   |

| market                                                                                          |

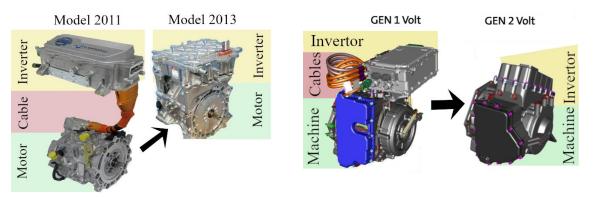

| Figure 7 – Adoption of integration approach in commercial EV drive units (left -2011 and        |

| 2013 model Nissan Leaf[14], right – Gen 1 and Gen 2 Chevy Volt model[15])22                     |

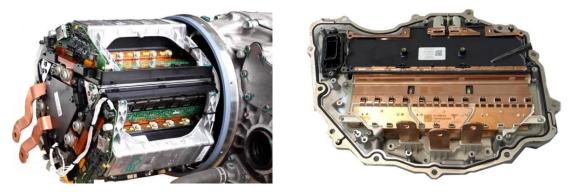

| Figure 8 - Examples of commercial integrated inverters demonstrating different structure        |

| design (radial 3 boards Tesla Model S - left, flat inverter Tesla Model 3 - right)23            |

| Figure 9 - HT IMD can eliminate additional gears or power cables in case of HT                  |

| environment                                                                                     |

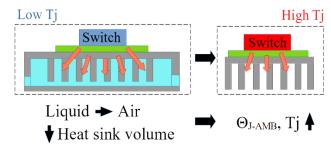

| Figure 10 – Smaller heatsink (or the change of cooling type) might save volume in expense       |

| of low junction temperature                                                                     |

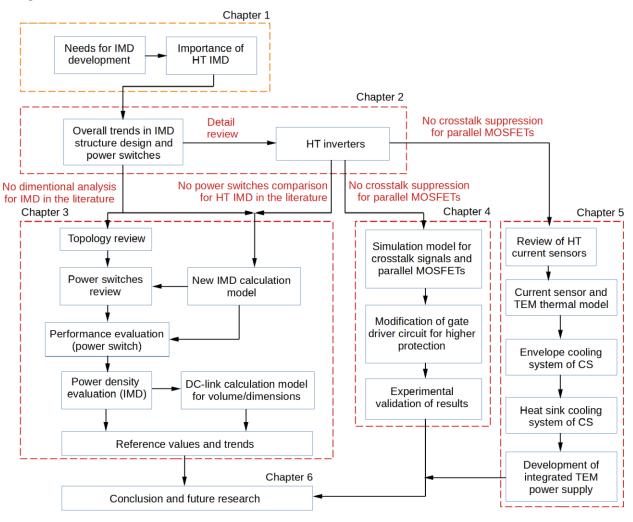

| Figure 11 – Diagram with links between the thesis chapters                                      |

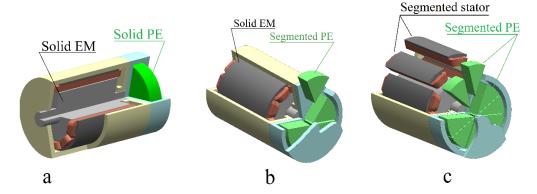

| Figure $12 - IMD$ classification based on its structure modularity (a - IMD, b - ISMD with      |

| segmented PE, c - IMMD)                                                                         |

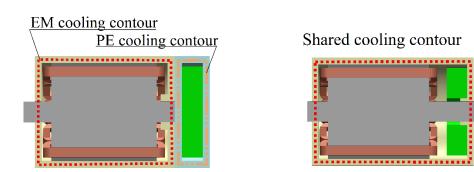

| Figure 13 – Examples of external (left) and inner (right) location of PE                        |

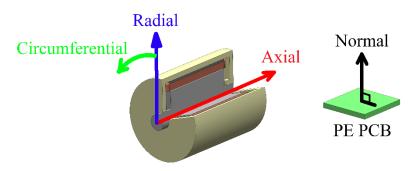

| Figure 14 - Classification for different orientations of PE PCB's normal vector with respect    |

| to the machine's axis of rotation                                                               |

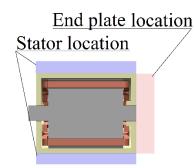

| Figure 15 – Examples of end plate and stators accommodations of PE elements                     |

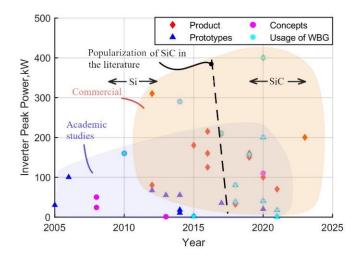

| Figure 16 - Inverter peak power for industry/academic designs over 2005- 2022 and usage         |

| of WBG components                                                                               |

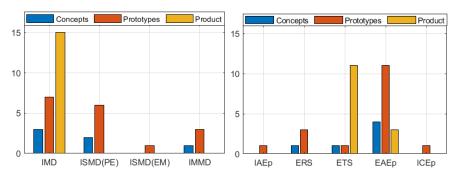

| Figure 17 – Distribution of IMD structures                                                      |

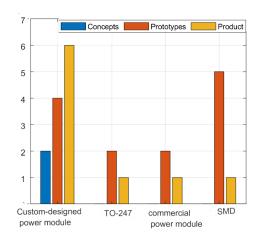

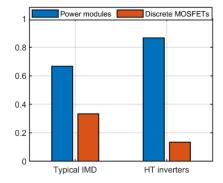

| Figure 18 – Distribution of switching devices in IMD reviewed                                   |

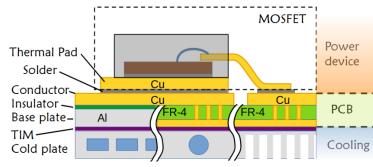

| Figure 19 - Reported cooling stack for IMD with discrete components (IMS with water             |

| cooling[29], FR-4 with liquid cooling[38], FR-4 with air cooling[40])40                            |

|----------------------------------------------------------------------------------------------------|

| Figure 20 – Example of ceramic PCB for power electronics of IMD [42]40                             |

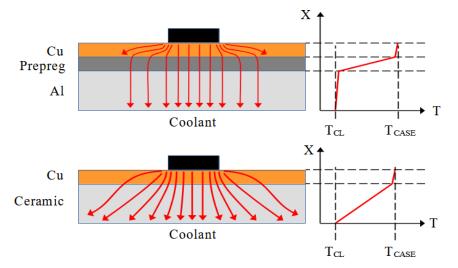

| Figure 21 – Heat spreading and temperature distribution in IMS and ceramic PCBs with               |

| typical value of $\Theta HS - A$ for water cooled cold plates ( $\Theta HS - A$ is comparable with |

| OCeramic)                                                                                          |

|                                                                                                    |

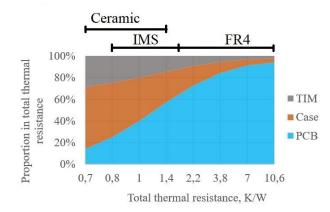

| Figure 22 – Total thermal resistance for SMT MOSFET with different PCB material ( $\Theta J$ –     |

| $C = 0.4 KW, \Theta TIM = 0.5KW, SPCB AREA = 1.5 cm2)41$                                           |

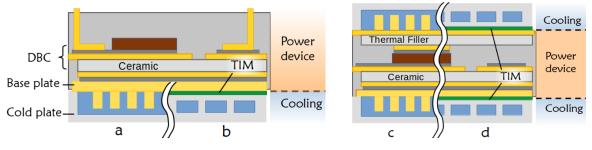

| Figure 23 – Typical cooling technologies for power modules (a, b – single side cooling; c,         |

| d– double side cooling; a, c – pin fin direct cooling; b, d – indirect cooling)42                  |

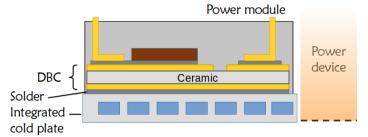

| Figure 24 - Typical cooling stack for power modules with integrated cold plate43                   |

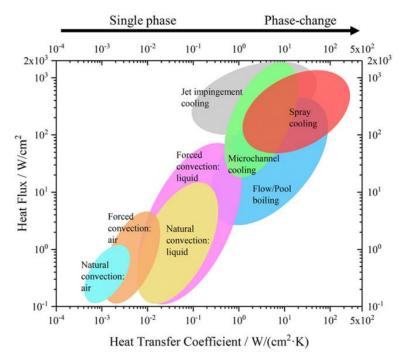

| Figure 25 – Comparison of different heat transfer methods [65]45                                   |

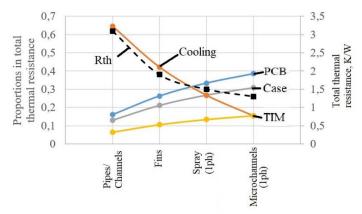

| Figure 26 – Influence of cooling method on total thermal resistance for SMT MOSFET with            |

| IMS (heat transfer coefficients are typical for 1GPM coolant flowrate)46                           |

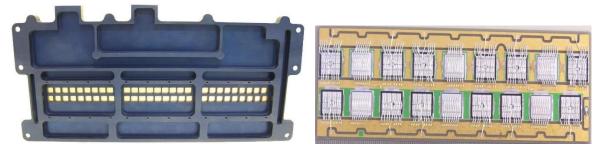

| Figure 27 - Bottom side of RINI inverter with windows for direct spray cooling (golden             |

| colour) [68] and one of its inner DBC boards with array of parallel devices, top view[69]48        |

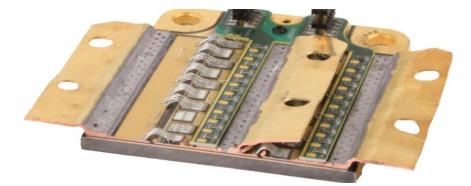

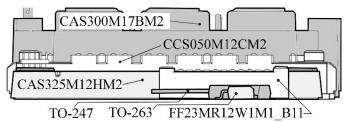

| Figure 28 – Section of power module CAS325M12HM249                                                 |

| Figure 29 – OEM 300kW inverter CRD300DA12E-XM3 by WolfSpeed[79]50                                  |

| Figure 30 – Different packages of semiconductor power switches                                     |

| Figure 31 – Usage of different power devices in typical IMD and HT inverters                       |

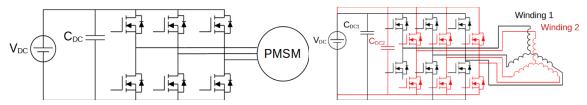

| Figure 32 – 3-phase 2-level VSI (single drive – left, double channels - right)                     |

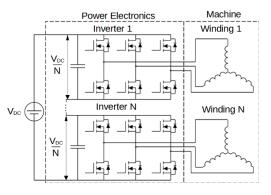

| Figure 33 – Serial connection of 3-phase 2-level VSI                                               |

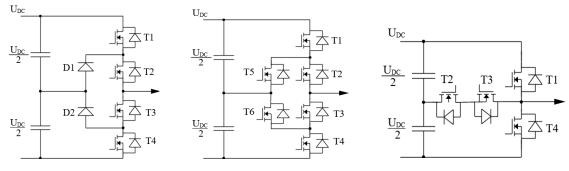

| Figure 34 - 3-level topologies (from the left NPC, ANPC, and TNPC)                                 |

| Figure 35 – Power modules with 106×62 form-factor (pin layout is completely different)57           |

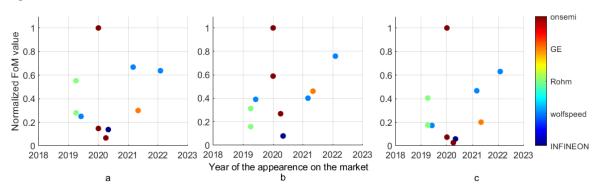

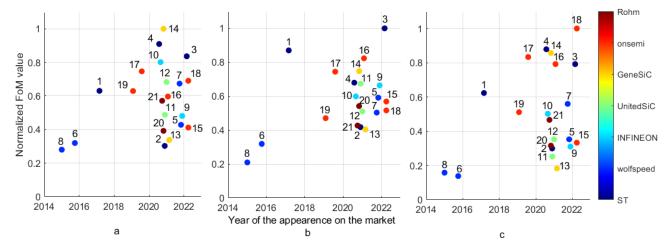

| Figure 36 – Different FOM variants for power modules (a – FOM, b – FOMVol, c –                     |

| <i>FOMout</i> )                                                                                    |

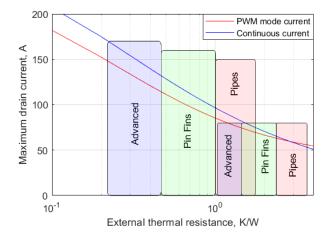

| Figure 37 – Maximum current vs case-ambient thermal resistance (left group – with AlN              |

| heat spreader, right group – mica insulation pad/grease, MOSFET - IMZA120R007M1H,                  |

| flowrate 1GPM)                                                                                     |

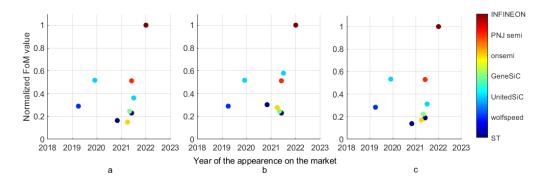

| Figure 38 - Different FOM variants for THT MOSFETs (a – FOM, b – FOMcurrent, c –                   |

| FOMout)                                                                                            |

|                                                                                                    |

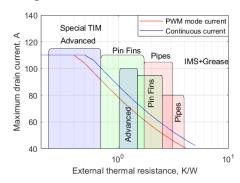

| Figure 39 - Maximum RMS current vs case-ambient thermal resistance (left group – with              |

| AlN heat spreader, right group - IMS PCB, MOSFET - SCT011H75G3AG) and appropriate          |

|--------------------------------------------------------------------------------------------|

| cooling techniques (flowrate 1GPM)                                                         |

| Figure 40 - Different FOM variants for SMT MOSFETs (a - FOM, b - FOMcurrent, c -           |

| <i>FOMout</i> )                                                                            |

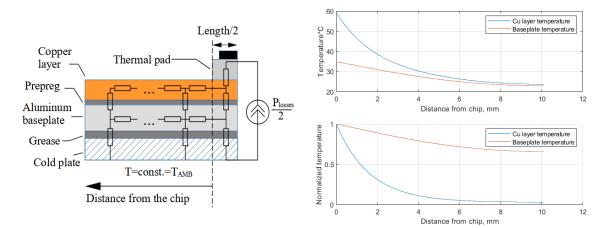

| Figure 41 – Thermal model of IMS PCB and relative temperatures of different layers with    |

| distance from the thermal pad ( <i>PLOSS</i> = 20 <i>W</i> , $Tamb = 0 \ \mathcal{C}$ )    |

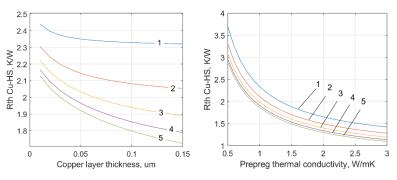

| Figure 42 – Effect of heat spreader size (figures are distances between edge of device and |

| edge of PCB), copper thickness, and prepreg thermal conductivity on case-heatsink thermal  |

| resistance                                                                                 |

| Figure 43 – Layout for SMT (TO-263-7) and THT (TO-247) components72                        |

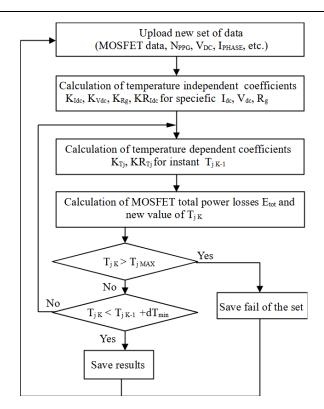

| Figure 44 – Flowchart for the calculation of junction temperature                          |

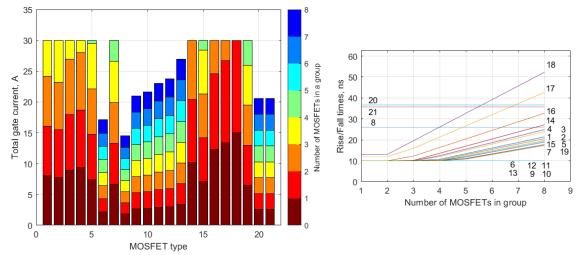

| Figure 45 – Total gate current and rise/fall time for different types of SMT MOSFETs74     |

| Figure 46 – Total gate current and rise/fall time for different types of THT MOSFETs74     |

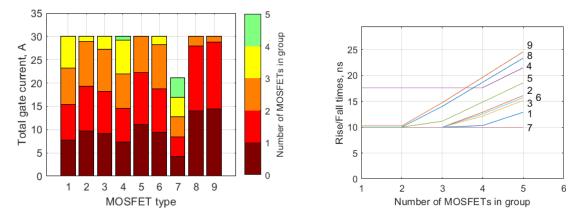

| Figure 47 - Total gate current and rise/fall time for different types of power modules     |

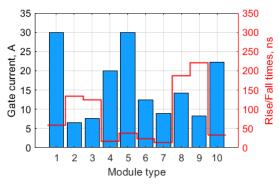

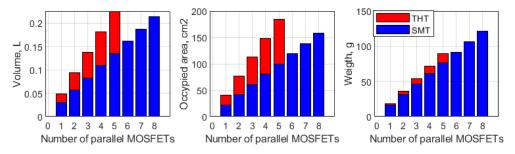

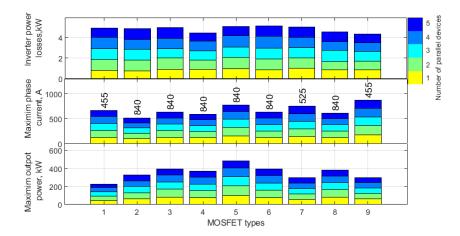

| Figure 48 – Results of dimension analysis for whole range of parallel devices              |

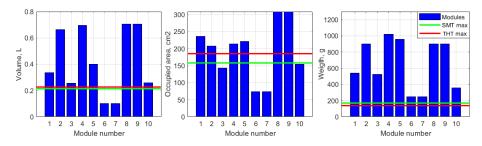

| Figure 49 - Results of dimension analysis for power modules (maximum values of SMT and     |

| THT devices are added for comparison)                                                      |

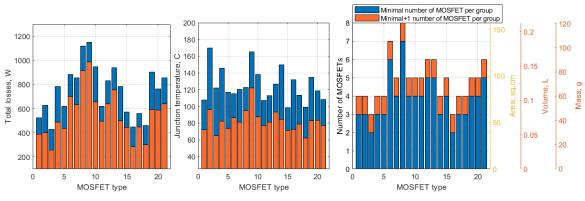

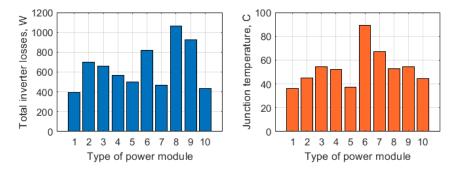

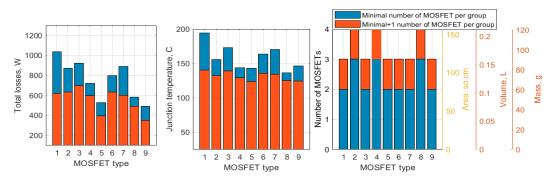

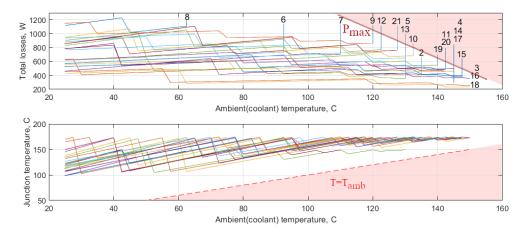

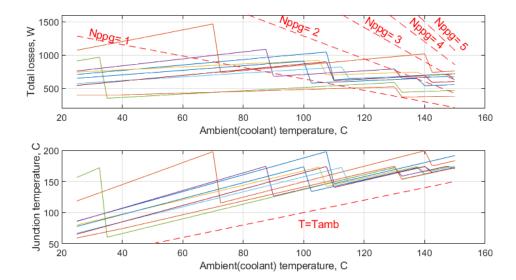

| Figure 50 – Total losses and junction temperature of SMT MOSFETs in Scenario 1             |

| ( <i>TAMB</i> =25°C)                                                                       |

| Figure 51 - Total losses and junction temperature of THT MOSFETs in Scenario 1             |

| ( <i>TAMB</i> =25°C)                                                                       |

| Figure 52 - Total losses and junction temperature of power modules in Scenario 1           |

| ( <i>TAMB</i> =25°C)                                                                       |

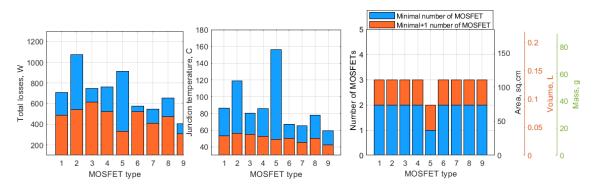

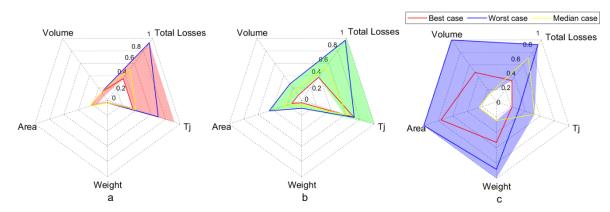

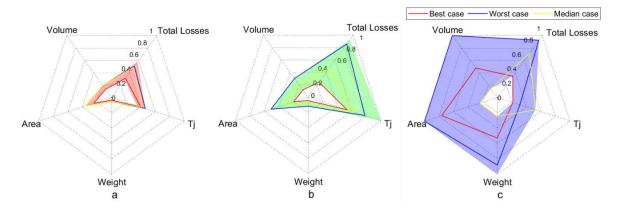

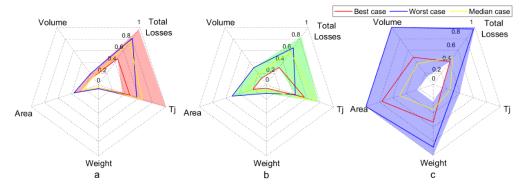

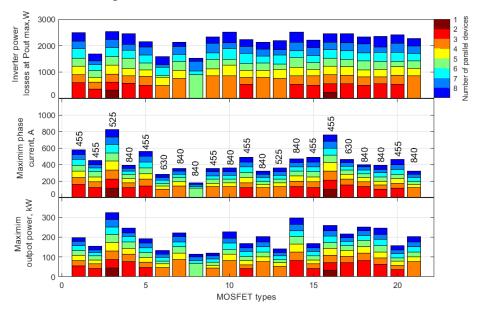

| Figure 53 – Normalized analysis results for the minimum number of parallel devices at      |

| $TAMB=25^{\circ}C (a - THT, b - SMT, c - power modules)$                                   |

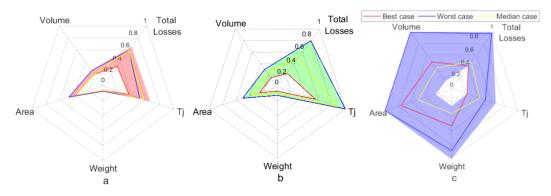

| Figure 54 – Normalized analysis results for the (minimum+1) number of parallel devices     |

| $TAMB=25^{\circ}C$ (a – THT, b – SMT, c – power modules)                                   |

| Figure 55 - Total losses and junction temperature of SMT MOSFETs in Scenario 1             |

| $(TAMB=105^{\circ}C)$                                                                      |

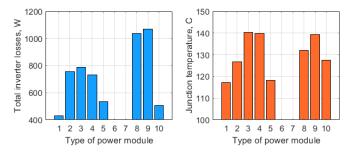

| Figure 56 - Total losses and junction temperature of THT MOSFETs in Scenario 1             |

| $(TAMB=105^{\circ}C)$                                                                      |

| (1711-10-105 C)                                                                            |

| Figure 57 - Total losses and junction temperature of power modules in Scenario 1                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ( <i>TAMB</i> =105°C)80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 58 - Normalized analysis results for the minimum number of parallel devices                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <i>TAMB</i> =105°C (a – THT, b – SMT, c – power modules)80                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 59 - Normalized analysis results for the (minimum+1) number of parallel devices                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <i>TAMB</i> =105°C (a – THT, b – SMT, c – power modules)81                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

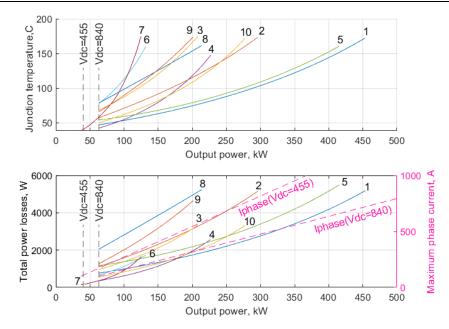

| Figure 60 - Total losses and junction temperature of SMT MOSFETs in Scenario 1                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ( <i>TAMB</i> =25÷150°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 61 - Total losses and junction temperature of THT MOSFETs in Scenario 1                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ( <i>TAMB</i> =25÷150°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

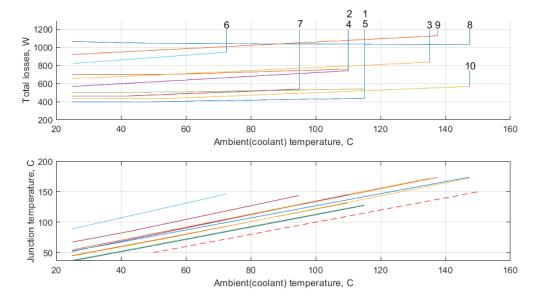

| Figure 62 - Total losses and junction temperature of power modules in Scenario 1                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ( <i>TAMB</i> =25÷150°C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 63 – Simulation results of SMT MOSFET with maximum output power TAMB=25°C                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 64 – Simulation results of THT MOSFET with maximum output power TAMB=25°C                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 65 - Simulation results of power modules with maximum output power TAMB=25°C                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

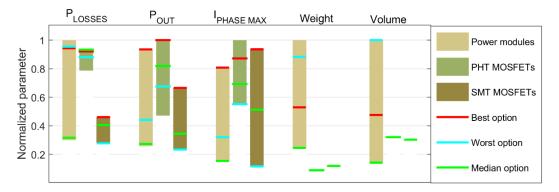

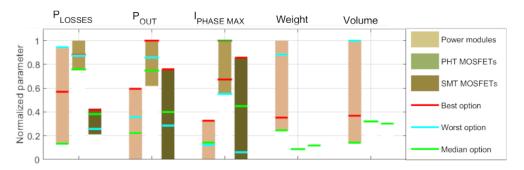

| Figure 66 - Normalized analysis results for Scenario 2 conditions with TAMB=25°C86                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Eigen (7 Circulation and a COMT MOSEET with marine and and                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 67 - Simulation results of SMT MOSFET with maximum output power                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 67 - Simulation results of SM1 MOSFE1 with maximum output power $TAMB=105^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <i>TAMB</i> =105°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TAMB=105°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TAMB=105°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TAMB=105°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

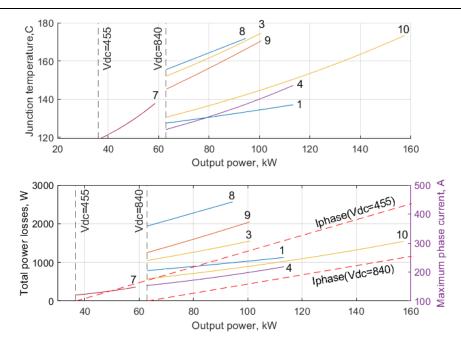

| $TAMB=105^{\circ}C$ 87Figure 68- Simulation results of THT MOSFET with maximum output power $TAMB=105^{\circ}C$ 88Figure 69 - Simulation results of power modules with maximum output power88 $TAMB=105^{\circ}C$ 89                                                                                                                                                                                                                                                                                                      |

| $TAMB=105^{\circ}C$ 87Figure 68- Simulation results of THT MOSFET with maximum output power $TAMB=105^{\circ}C$ 88Figure 69 - Simulation results of power modules with maximum output power89Figure 70 - Normalized analysis results for Scenario 2 conditions with $TAMB=105^{\circ}C$ 89                                                                                                                                                                                                                                |

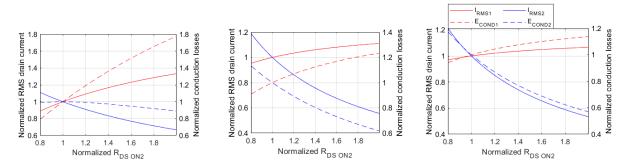

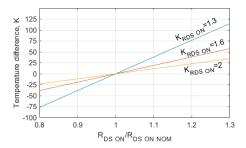

| $TAMB=105^{\circ}C$ 87Figure 68- Simulation results of THT MOSFET with maximum output power $TAMB=105^{\circ}C$ 88Figure 69 - Simulation results of power modules with maximum output power89 $TAMB=105^{\circ}C$ 89Figure 70 - Normalized analysis results for Scenario 2 conditions with $TAMB=105^{\circ}C$ 89Figure 71 - Difference in drain current and conduction losses due to disbalance of $RDS ON$                                                                                                              |

| TAMB=105°C       87         Figure 68- Simulation results of THT MOSFET with maximum output power TAMB=105°C       88         Figure 69 - Simulation results of power modules with maximum output power       88         Figure 69 - Simulation results of power modules with maximum output power       89         Figure 70 - Normalized analysis results for Scenario 2 conditions with TAMB=105°C       89         Figure 71 - Difference in drain current and conduction losses due to disbalance of RDS ON       91 |

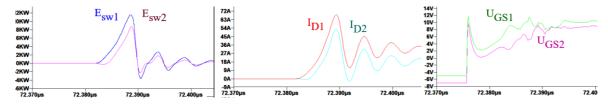

| $2V$ and $\Delta ESW ON = 42\mu J - 25\mu J = 17\mu J$                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

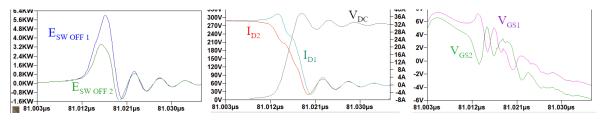

| Figure 74 – Simulated turn-off of two parallel SMT MOSFET c3m0065090j with $\Delta VTH =$                                                                                                                                                                                                                                                                                                                                                  |

| $2V$ and $\Delta ESW \ OFF = 23\mu J - 13\mu J = 10\mu J$                                                                                                                                                                                                                                                                                                                                                                                  |

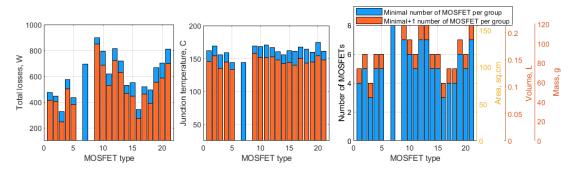

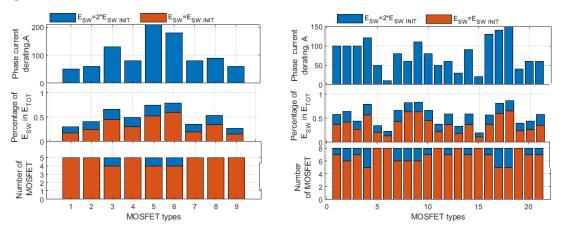

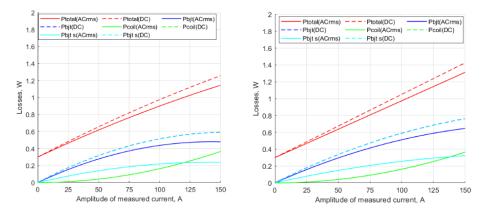

| Figure 75 – Influence of doubled switching losses on THT (left) and SMT (right) devices for                                                                                                                                                                                                                                                                                                                                                |

| $TAMB = 25^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                       |

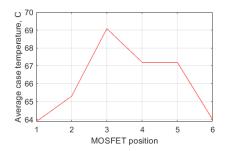

| Figure 76 - Measured average case temperature of 6 MOSFETs connected in parallel                                                                                                                                                                                                                                                                                                                                                           |

| (package TO-220 attached to IMS and water cooling, <i>PMOSFET</i> =15W)95                                                                                                                                                                                                                                                                                                                                                                  |

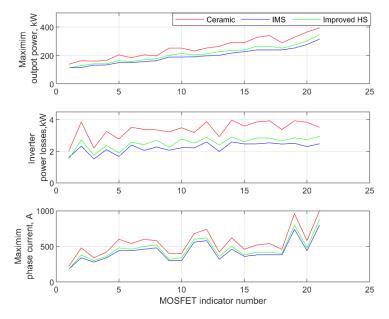

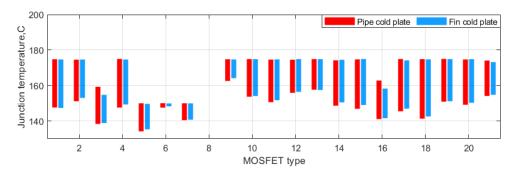

| Figure 77 – Effect of ceramic PCB and improved cooling on performance of inverter with                                                                                                                                                                                                                                                                                                                                                     |

| SMT MOSFETs96                                                                                                                                                                                                                                                                                                                                                                                                                              |

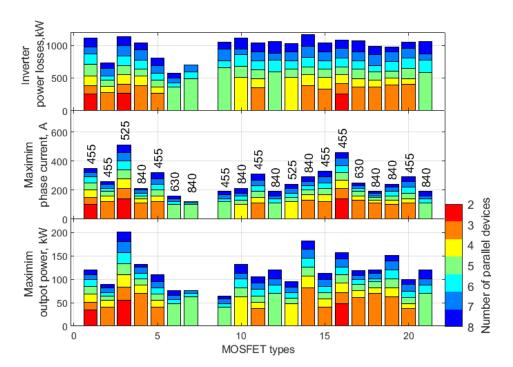

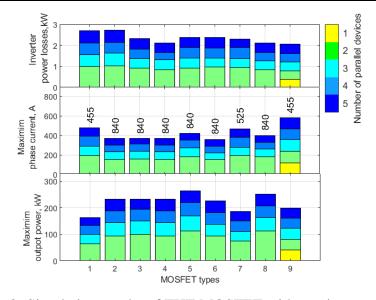

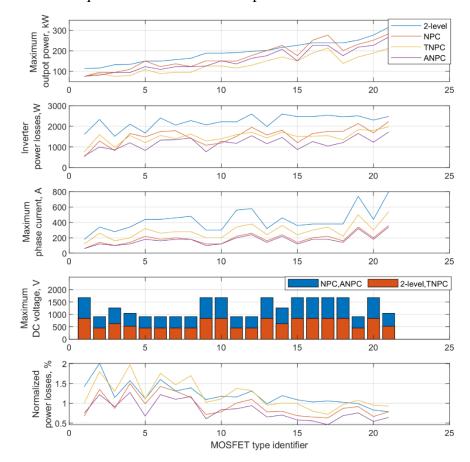

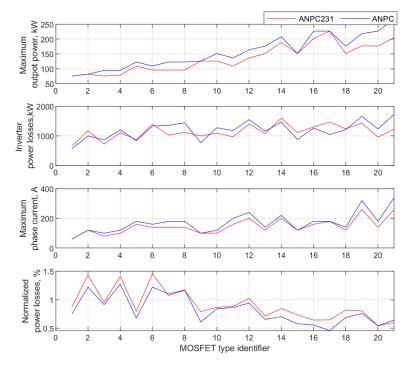

| Figure 78 – Comparison between 2-level and 3-level topologies (MOSFET type identifier is                                                                                                                                                                                                                                                                                                                                                   |

| different from previous chapters)99                                                                                                                                                                                                                                                                                                                                                                                                        |

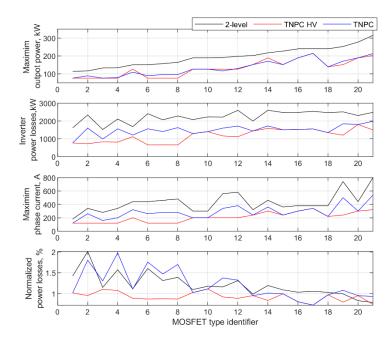

| Figure 79 – Simulation results of modified TNPC topology100                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 80 – Performance of ANPC topology with 25% reduction of MOSFET quantity101                                                                                                                                                                                                                                                                                                                                                          |

| Figure 81 - Summary diagram of performance comparison between 2- and 3-level inverter                                                                                                                                                                                                                                                                                                                                                      |

| topologies                                                                                                                                                                                                                                                                                                                                                                                                                                 |

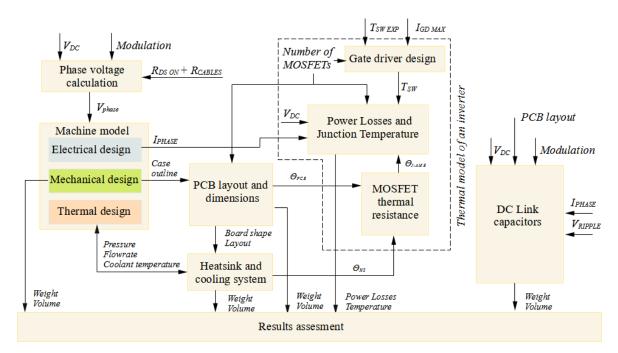

| Figure 82 – Relation between machine's mass and phase current of motors used104                                                                                                                                                                                                                                                                                                                                                            |

| Figure 83 – Flowchart of IMD combined calculation model104                                                                                                                                                                                                                                                                                                                                                                                 |

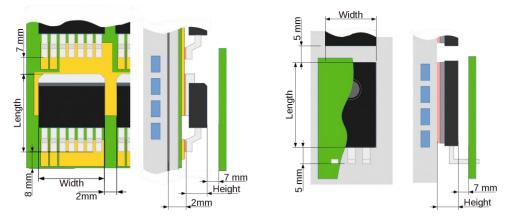

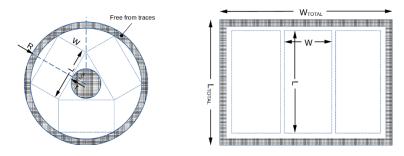

| Figure 84 – Two different shapes of PE PCB105                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 85 – Layout structure of round (left) and rectangular (right) PCB105                                                                                                                                                                                                                                                                                                                                                                |

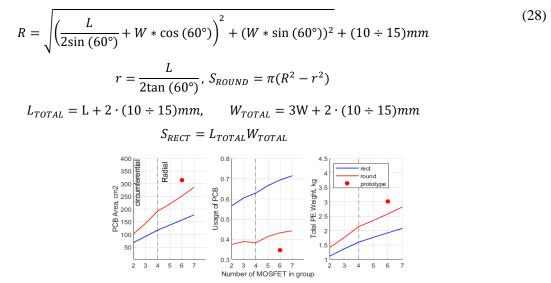

| Figure 86 - Comparison of round and rectangular PCB shapes for different number of                                                                                                                                                                                                                                                                                                                                                         |

| transistors in a group                                                                                                                                                                                                                                                                                                                                                                                                                     |

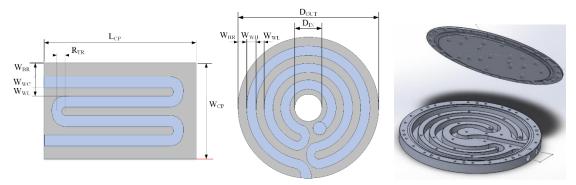

| Figure 87 – Structure of water channels for different PCB shapes106                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |

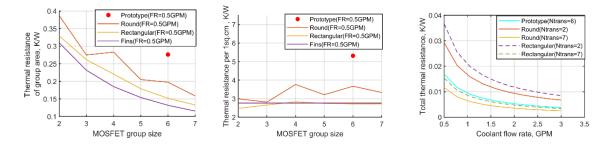

| Figure 88 – Characteristics of a cold plate with different Ntrans, layout, flow rate and                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 88 – Characteristics of a cold plate with different Ntrans, layout, flow rate and                                                                                                                                                                                                                                                                                                                                                   |

| Figure 88 – Characteristics of a cold plate with different Ntrans, layout, flow rate and cooling techniques                                                                                                                                                                                                                                                                                                                                |

| Figure 88 – Characteristics of a cold plate with different Ntrans, layout, flow rate and cooling techniques                                                                                                                                                                                                                                                                                                                                |

| Figure 88 – Characteristics of a cold plate with different Ntrans, layout, flow rate and cooling techniques                                                                                                                                                                                                                                                                                                                                |

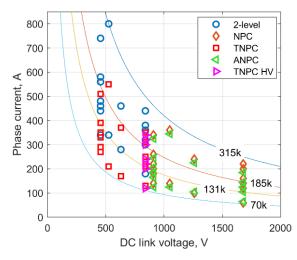

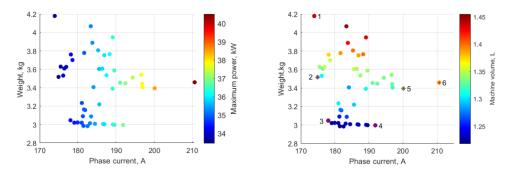

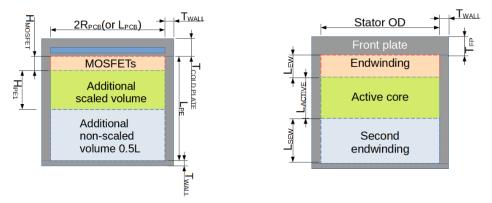

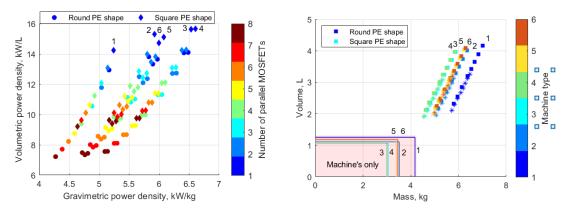

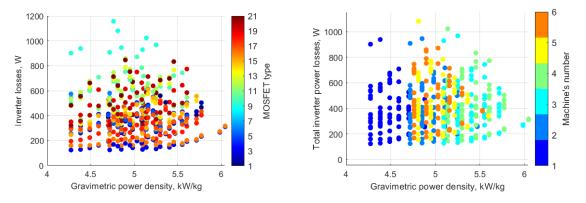

| Figure 88 – Characteristics of a cold plate with different Ntrans, layout, flow rate and cooling techniques.       108         Figure 89 – Scheme for inverter (left) and machine (right) volume calculation.       109         Figure 90 – Possible values for power density with different machines (right) and number of parallel devices (left)       110                                                                              |

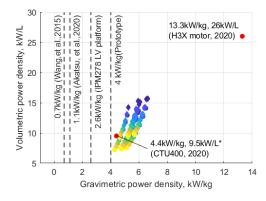

| Figure 88 – Characteristics of a cold plate with different Ntrans, layout, flow rate and cooling techniques.       108         Figure 89 – Scheme for inverter (left) and machine (right) volume calculation.       109         Figure 90 – Possible values for power density with different machines (right) and number of parallel devices (left)       110         Figure 91 – Comparison with characteristics of other IMDs.       110 |

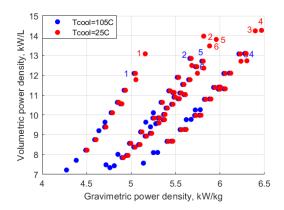

| Figure 88 – Characteristics of a cold plate with different Ntrans, layout, flow rate and cooling techniques                                                                                                                                                                                                                                                                                                                                |

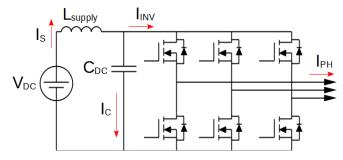

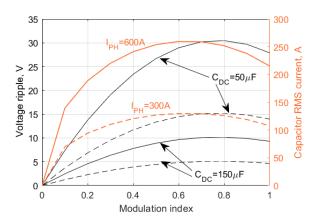

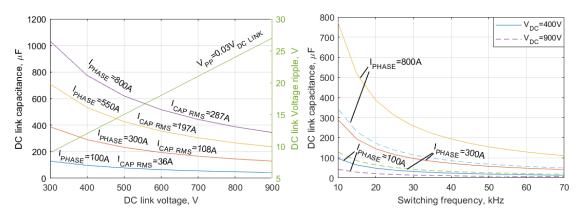

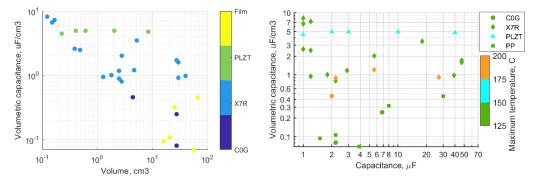

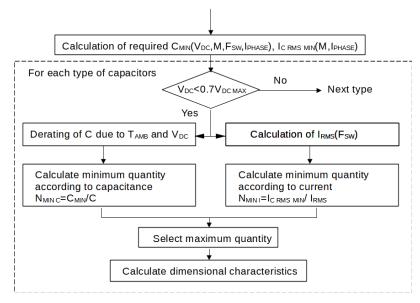

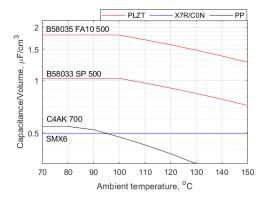

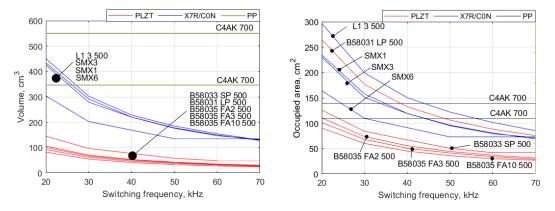

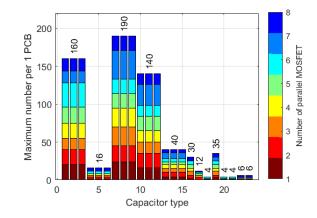

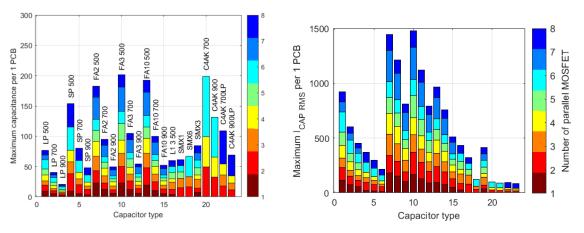

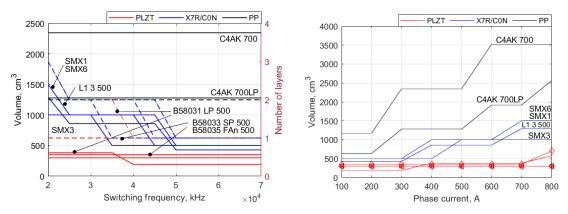

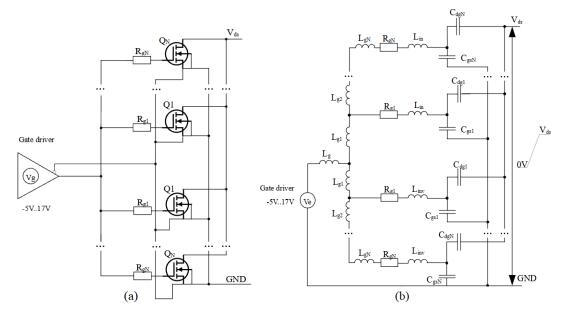

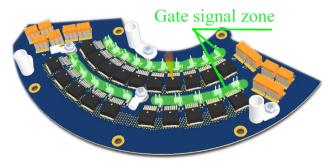

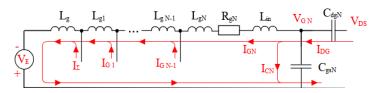

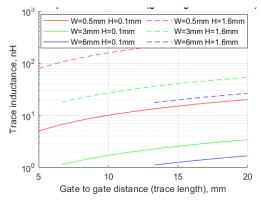

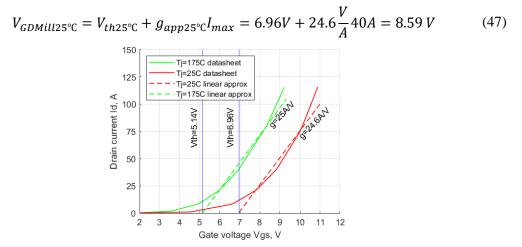

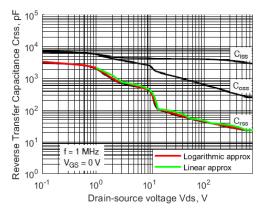

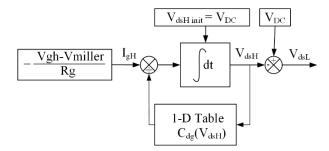

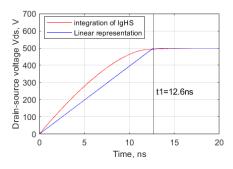

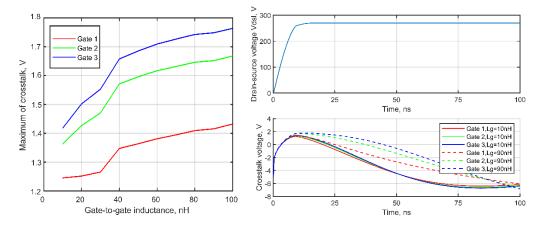

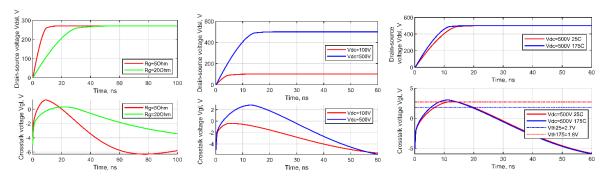

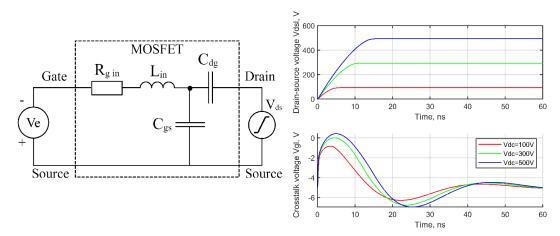

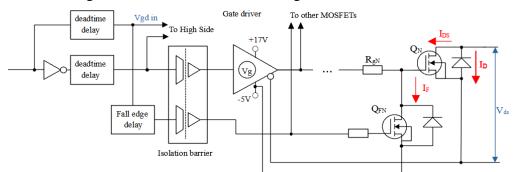

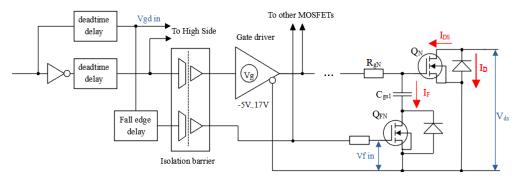

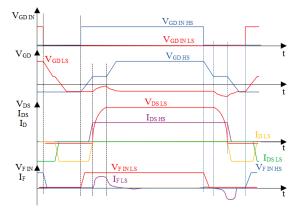

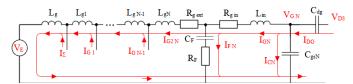

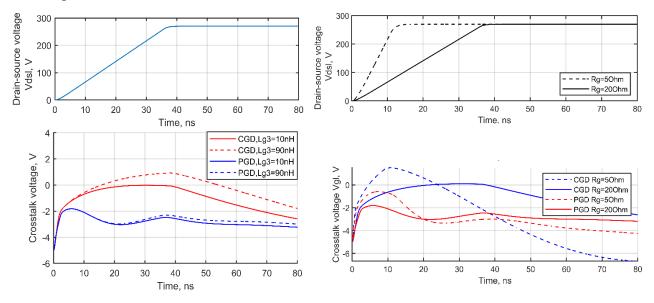

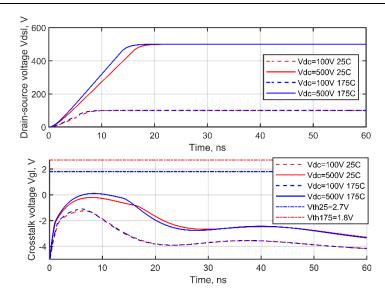

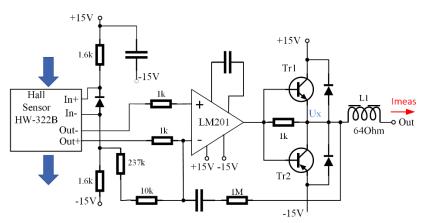

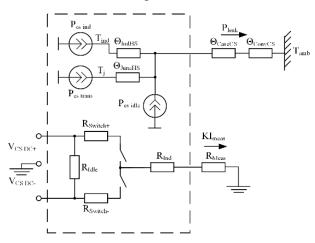

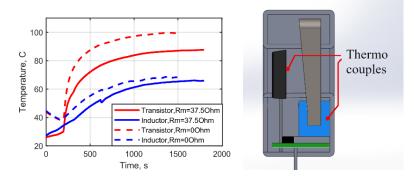

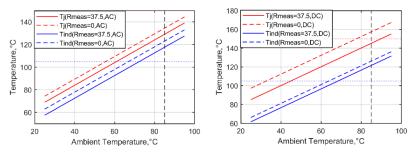

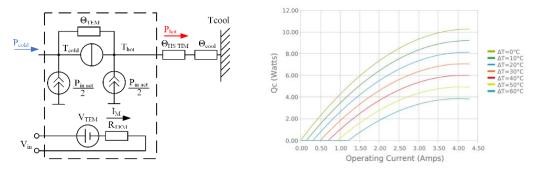

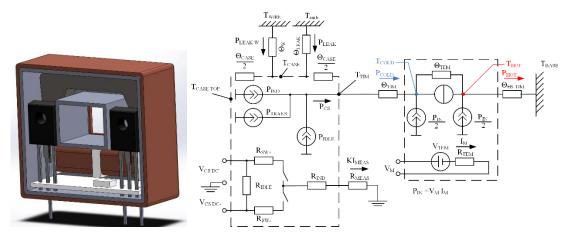

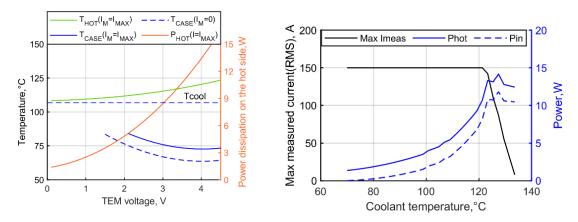

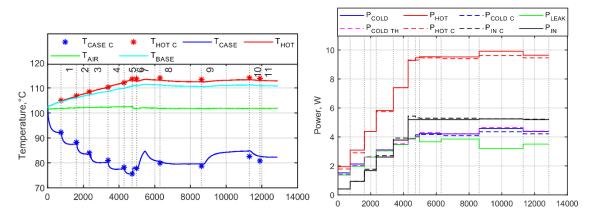

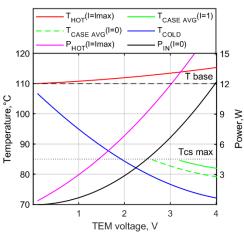

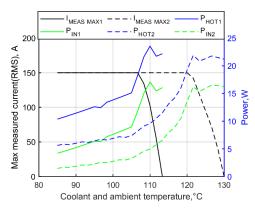

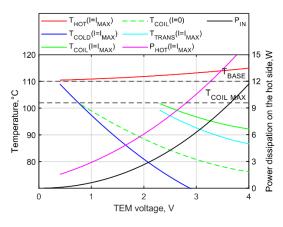

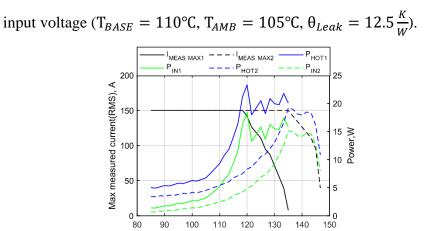

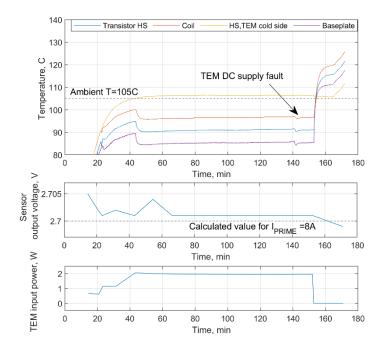

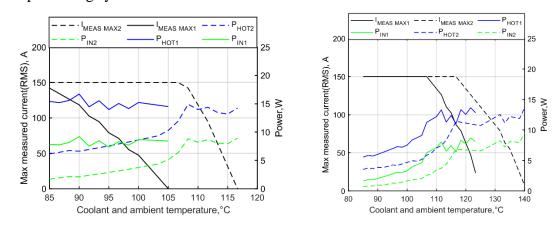

Figure 95 – Currents involved in operation of DC-link capacitor of 2 level 3 phase topology. Figure 96 – Voltage ripples and capacitor RMS current for different values of modulation index, phase current (solid line – 600A, dash line – 300A) and capacitance at FSW = 50kHzFigure 97 – Required value of DC-link capacitor to maintain specific level (3% of VDC) of Figure 98 – Distribution of volumetric capacitance for HT HV capacitors......116 Figure 99 – Flowchart of DC-link capacitor sizing process ......116 Figure 100 – Temperature related derating of capacitance for different materials......117 Figure 101 – Total volumes and areas of DC-link capacitor within specified range of switching frequency (M=1, VDC=400V, IPHASE = 300A).....117 Figure 103 – Maximum total capacitance and RMS current per PCB......118 Figure 104 – Volume of DC-link capacitor bank for various switching frequency and phase current (solid line – volume, dash line – the number of PCBs, M=1, V=400V).....119 Figure 105 – Schematic of a distributed gate drive circuit (a) and its simplified model (b)124 Figure 106 – Example of parallel MOSFET (10 in a group) and layout of gate traces. .....124 Figure 108 – Gate-to-gate trace inductances with different lengths, widths, and PCB Figure 109 - Transfer characteristics and its linear approximation at different junction temperatures......127 Figure 110 – Comparison of logarithmic, linear approximations, and datasheet curve[104]. Figure 113 – Behaviour of crosstalk maximum for different gates and different trace Figure 114 – Crosstalk pulse with different gate resistance, drain voltage, and temperature (default conditions are Rgex=50hm, Lg=5nH, Vg=+17V/-5V, Id=40A, Tj=25°C).....130 Figure 115 – Inner gate voltage during crosstalk with shorted gate circuit (LS gate pin is

| shorted with Ve, HS gate has 50hm external resistor)131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 116 – Structure of a driver with external clamping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 117 – Structure of proposed gate driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 118 – Waveforms of voltages and currents during a single cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 119 – Equivalent circuit of gate circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 120 - Comparison of proposed gate driver (PGD) with conventional driver (CGD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| with different component values and voltage134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 121 - Crosstalk pulse with different gate resistance, drain voltage, and temperature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 122 – Maximum gate voltage at crosstalk with different Rf and Cf values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

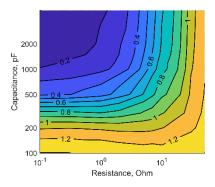

| $(Rg=50hm, Vds=270V, T=25^{\circ}C, V_{E NEG}=-5V)$ 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

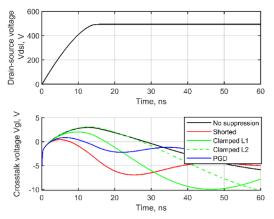

| Figure 123 – Crosstalk with different suppression techniques ( $R_{gexHS}$ =50hm, Tj=25C)136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 124 – Modified gate circuit (additional MOSFETs with capacitors)136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 125 - Comparison of the maximums of gate voltages during crosstalk and their                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| waveforms ( <i>Rgex</i> =100hm, <i>Vg</i> =+17V/-4.5V)137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

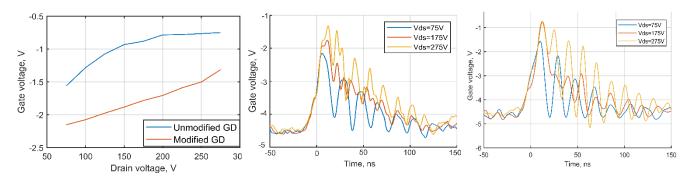

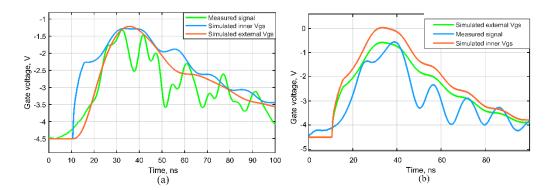

| Figure 126 – Comparison of experimental results and simulated results (a – PGD, b - CGD).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

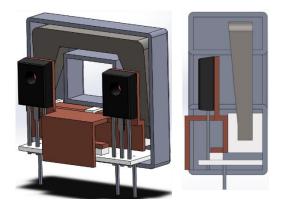

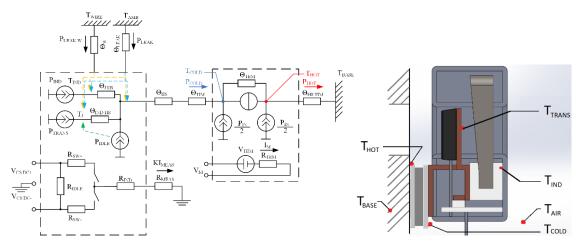

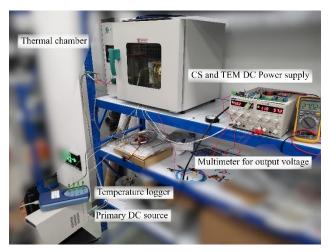

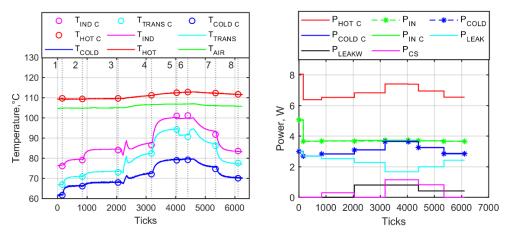

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |